# Digital Semiconductor SA-110 Microprocessor

# Technical Reference Manual

Order Number: EC-QPWLC-TE

**Revision/Update Information:**

This is revision C of a preliminary document. It supersedes the *Digital Semiconductor SA-110 Microprocessor Technical Reference Manual* (EC-QPWLB-TE). This manual is to be used in conjunction with *ARM Architectural Reference* (EC-QV44A-TE).

#### October 1996

While Digital believes the information included in this publication is correct as of the date of publication, it is subject to change without notice.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

© Digital Equipment Corporation 1996. All rights reserved. Printed in U.S.A.

Digital, Digital Semiconductor, and the DIGITAL logo are trademarks of Digital Equipment Corporation.

Digital Semiconductor is a Digital Equipment Corporation business.

ARM and ARM Powered are trademarks of Advanced RISC Machines Ltd.

All other trademarks and registered trademarks are the property of their respective owners.

# **SA-110 Microprocessor**

The Digital Semiconductor SA-110 Microprocessor (SA-110) is the first member of the StrongARM family of high-performance, low-power microprocessors. The SA-110 is an implementation of Advanced RISC Machines Ltd. (ARM) Version 4 architecture and offers significant advances in microprocessor design. The SA-110 has been designed to further extend the ARM family as the world's leading source of low-power, high-performance RISC processors for embedded consumer markets such as portable products and interactive digital video.

The SA-110 is a general-purpose, 32-bit RISC microprocessor with a 16KB instruction cache (Icache); a 16KB write-back data cache (Dcache); a write buffer; and a memory-management unit (MMU) combined in a single chip. The five-stage pipeline distributes tasks evenly over time to remove bottlenecks, ensuring high throughput for the core logic. The SA-110 offers high-level RISC performance, yet it provides minimal power consumption, making it ideal for portable, low-cost systems.

The SA-110 onchip MMU supports a conventional two-level page-table structure, with a number of extensions, which makes it ideal for embedded control systems and object-oriented systems. These features result in a high instruction throughput and impressive real-time response for a small and cost-effective chip.

#### **Features**

- High performance

- 115 Dhrystone 2.1 MIPS @100 MHz

- 185 Dhrystone 2.1 MIPS @160 MHz

- 192 Dhrystone 2.1 MIPS @166 MHz

- 230 Dhrystone 2.1 MIPS @200 MHz

- 268 Dhrystone 2.1 MIPS @233 MHz

- Low power (normal mode)

- 130 mW @1.65 V/100 MHz core/27 MHz bus

- 170 mW @ 1.65 V/160 MHz core/33 MHz bus

- 230 mW @ 2.0 V/166 MHz core/33 MHz bus

- 330 mW @ 2.0 V/200 MHz core/50 MHz bus

- 420 mW @ 2.0 V/233 MHz core/66 MHz bus

- Internal phase-locked loop (PLL)

- 3.68 or 3.56 MHz external reference oscillator

- Idle and sleep power-down modes

- Big and little endian operating modes

- 3.3-V I/O interface

#### **Applications**

- Portable products

- Personal Digital Assistants (PDAs)

- Smart phones

- Digital cameras

- Organizers

- Bar-code scanners

- · Interactive digital media

- Digital set-top devices

- Interactive TV

- Video game players

- 144-pin thin quad flat pack (TQFP)

- 32-way set-associative caches

- 16KB instruction cache

- 16KB write-back data cache

- 32-entry memory-management units

- Maps 4KB, 64KB, or 1MB

- Write buffer

- 8 entry 16-bytes each

- Early termination 32-bit multiplier

- 32-bit accumulation (2-4 cycles)

- 64-bit accumulation (3-5 cycles)

- Memory bus

- Asynchronous or synchronous

- 0-33 MHz @ 100 MHz

- 0-53 MHz @ 160 MHz

- 0-53 MHz @ 166 MHz

- 0-66 MHz @ 200 MHz0-66 MHz @ 233 MHz

- Embedded control

- Internetworking: routers, bridges, LAN switches

- Office automation: printers, scanners, copiers

- Telecommunication: PBX, Cellular Base Station

- Storage peripherals: drive and RAID controllers

- PC add-ins: intelligent I/O cards, LAN/WAN

- Network computers

- Tablet intranet products

- Internet appliances

# **Table of Contents**

| 1.0 Introduction                                   | . 1 |

|----------------------------------------------------|-----|

| 1.1 ARM Architecture                               | .2  |

| 1.1.1 26-Bit Mode                                  | .2  |

| 1.1.2 Coprocessors                                 | .2  |

| 1.1.3 Memory Management                            | .2  |

| 1.1.4 Instruction Cache                            | .2  |

| 1.1.5 Data Cache                                   | .2  |

| 1.1.6 Write Buffer                                 | .2  |

| 1.2 Block Diagram                                  | .3  |

| 1.3 Functional Diagram                             | .4  |

| 2.0 Signal Description                             | .5  |

| 3.0 ARM Implementation Options                     | .8  |

| 3.1 Big and Little Endian                          |     |

| 3.2 Exceptions                                     |     |

| 3.2.1 Reset                                        |     |

| 3.2.2 Abort                                        | 9   |

| 3.2.3 Vector Summary                               |     |

| 3.2.4 Exception Priorities                         |     |

| 3.2.5 Interrupt Latencies                          |     |

| 3.3 Coprocessors                                   |     |

| 4.0 Instruction Set                                |     |

| 4.1 Instruction Set                                |     |

| 4.2 Instruction Timings                            |     |

| 5.0 Configuration                                  |     |

| 5.1 Internal Coprocessor Instructions              |     |

| 5.2 Registers                                      |     |

| 5.2.1 Register 0 – ID                              |     |

| 5.2.2 Register 1 – Control                         |     |

| 5.2.3 Register 2 – Translation Table Base          |     |

| 5.2.4 Register 3 – Domain Access Control           |     |

| 5.2.5 Register 4 – Reserved                        |     |

| 5.2.6 Register 5 – Fault Status                    |     |

| 5.2.7 Register 6 – Fault Address                   |     |

| 5.2.8 Register 7 – Cache Control Operations        |     |

| 5.2.9 Register 8 – TLB Operations                  |     |

| 5.2.10 Registers 9 -14 Reserved                    |     |

| 5.2.11 Registers 15 – Test, Clock and Idle Control |     |

| 5.2.11.1 Icache LFSR Controls                      |     |

| 5.2.11.2 Clock Controls                            |     |

| 6.0 Caches and Write Buffer 1                      |     |

| 6.1 Instruction Cache (Icache)                     |     |

| 6.1.1 Icache Operation                             |     |

| 6.1.2 Icache Validity                              |     |

# **Table of Contents**

|         | 6.1.2.1 Software Icache Flush                                    | 19 |

|---------|------------------------------------------------------------------|----|

|         | 6.1.3 Icache Enable/Disable and Reset                            | 19 |

|         | 6.1.3.1 Enabling the Icache                                      | 19 |

|         | 6.1.3.2 Disabling the Icache                                     |    |

| 6.2     | Data Cache (Dcache)                                              |    |

|         | 6.2.1 Cacheable Bit – C                                          |    |

|         | 6.2.2 Bufferable Bit - B.                                        |    |

|         | 6.2.3 Dcache Operation                                           |    |

|         | 6.2.3.1 Cacheable Reads $C = 1$                                  |    |

|         | 6.2.3.2 Noncacheable Reads $C = 0$                               |    |

|         | 6.2.4 Dcache Validity                                            |    |

|         | 6.2.4.1 Software Deache Flush                                    |    |

|         | 6.2.4.2 Doubly Mapped Space                                      |    |

|         | 6.2.5 Dcache Enable/Disable and Reset                            |    |

|         | 6.2.5.1 Enabling the Deache                                      |    |

|         | 6.2.5.2 Disabling the Deache                                     |    |

| 6.3     | Write Buffer (WB)                                                |    |

| 0.0     | 6.3.1 Bufferable Bit                                             |    |

|         | 6.3.2 Write Buffer Operation                                     |    |

|         | 6.3.2.1 Writes to a Bufferable and Cacheable Location (B=1,C=1)  |    |

|         | 6.3.2.2 Writes to Bufferable and Noncacheable Location (B=1,C=0) |    |

|         | 6.3.2.3 Unbufferable Writes (B=0)                                |    |

|         | 6.3.3 Enabling the Write Buffer                                  |    |

|         | 6.3.4 Disabling the Write Buffer                                 |    |

| 7.0 M   | emory Management Unit (MMU)                                      |    |

|         | Overview                                                         |    |

| ,.1     | 7.1.1 MMU Registers                                              |    |

| 7.2     | MMU Faults and CPU Aborts                                        |    |

|         | External Aborts                                                  |    |

| 7.5     | 7.3.1 Cacheable Reads (Cache Line Fills)                         |    |

|         | 7.3.2 Buffered Writes                                            |    |

| 74      | Interaction of the MMU, Icache, Dcache and Write Buffer          |    |

|         | A-110 Clocking                                                   |    |

|         | SA-110 Operating Modes                                           |    |

|         | SA-110 Clocking                                                  |    |

| 0.2     | 8.2.1 Switching to Idle Mode                                     |    |

|         | 8.2.2 Switching to Sleep Mode                                    |    |

|         | 8.2.3 Core Clock Configuration - CCCFG                           |    |

|         | 8.2.4 Memory Clock Configuration - MCCFG                         |    |

|         | 8.2.5 Tester and Debug Clocks                                    |    |

| 9 () Br | is Interface                                                     |    |

|         | Bus Modes                                                        |    |

| 7.1     | 9.1.1 Standard and Enhanced Mode                                 |    |

| 92      | SA-110 Bus Stalls                                                |    |

|         | Cycle Types                                                      |    |

|         | Memory Access                                                    |    |

|         |                                                                  |    |

# **Table of Contents**

| 9.5 Read/Write                                         |    |

|--------------------------------------------------------|----|

| 9.6 Address Pipeline Enable (APE)                      | 32 |

| 9.7 Memory Access Types                                |    |

| 9.8 External Accesses                                  | 34 |

| 9.8.1 Unbuffered Writes / Noncacheable Reads           | 34 |

| 9.9 Buffered Write                                     | 35 |

| 9.10 Cache Line Fill                                   | 35 |

| 9.11 Read-Lock-Write                                   | 35 |

| 9.12 Stalling the Bus                                  | 36 |

| 9.13 Summary of Transactions                           | 37 |

| 9.13.1 Read Bursts                                     | 37 |

| 9.13.2 Write Bursts                                    | 37 |

| 9.13.3 Transaction Summary                             |    |

| 10.0 Boundary Scan Test Interface                      | 39 |

| 10.1 Overview                                          |    |

| 10.2 Reset                                             |    |

| 10.3 Pullup Resistors                                  | 41 |

| 10.4 nPWRSLP                                           |    |

| 10.5 Instruction Register                              |    |

| 10.6 Public Instructions                               | 41 |

| 10.6.1 EXTEST (00000)                                  |    |

| 10.6.2 SAMPLE/PRELOAD (00001)                          |    |

| 10.6.3 CLAMP (00100)                                   |    |

| 10.6.4 HIGHZ (00101)                                   |    |

| 10.6.5 IDCODE (00110)                                  |    |

| 10.6.6 BYPASS (11111)                                  |    |

| 10.7 Test Data Registers                               |    |

| 10.7.1 Bypass Register                                 |    |

| 10.7.2 SA-110 Device Identification (ID) Code Register |    |

| 10.7.3 SA-110 Boundary Scan (BS) Register              |    |

| 10.8 Boundary Scan Interface Signals                   |    |

| 11.0 dc Parameters                                     |    |

| 11.1 Absolute Maximum Ratings                          |    |

| 11.2 dc Operating Conditions                           |    |

| 11.3 dc Characteristics                                |    |

| 11.4 Power Supply Voltages and Currents                |    |

| 12.0 ac Parameters                                     |    |

| 12.1 Test Conditions                                   |    |

| 12.2 Module Considerations                             |    |

| 12.3 Main Bus Signals                                  |    |

| 12.4 SA-110 ac Parameters                              |    |

| 13.0 Physical Details                                  |    |

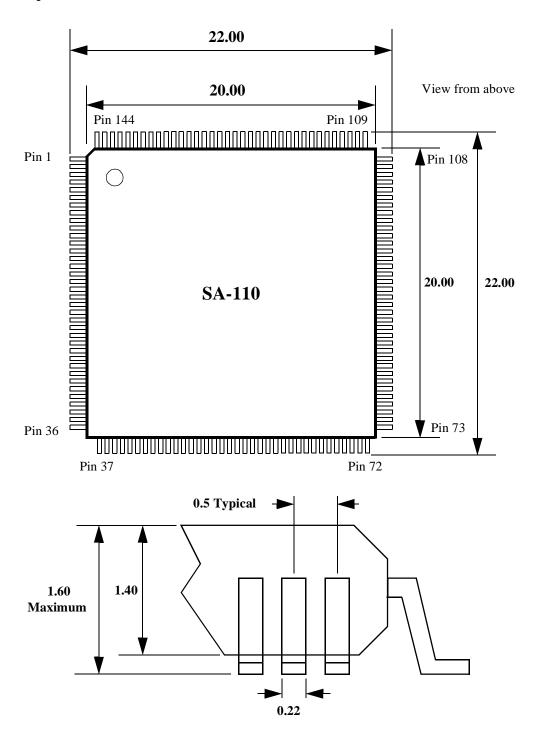

| 13.1 Pinout                                            | 63 |

| Support, Products and Documentation                    |    |

# **Figures**

# **Figures**

| 1 SA-110 Block Diagram                                  | 3  |

|---------------------------------------------------------|----|

| 2 Functional Diagram                                    | 4  |

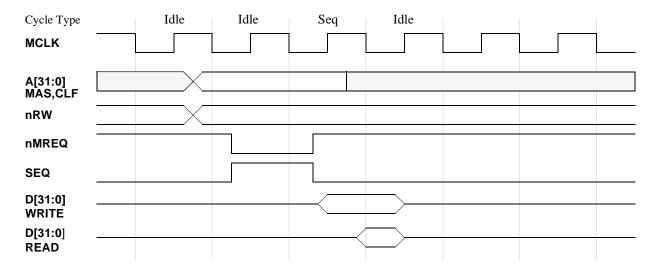

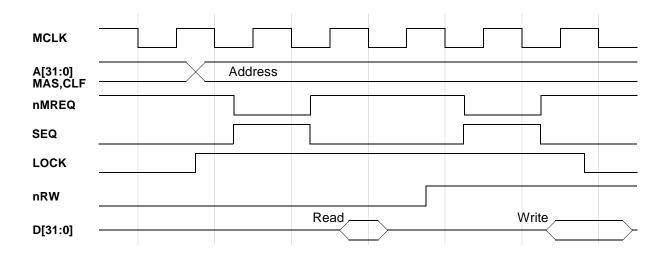

| 3 Read or Write (One Word)                              | 33 |

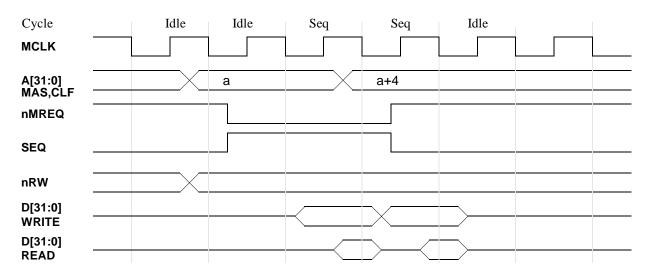

| 4 Sequential Read or Write (Two Word)                   | 33 |

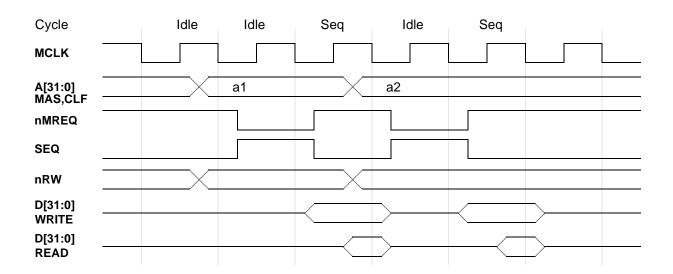

| 5 Two 1-Word Nonsequential Reads or Writes Back-to-Back | 34 |

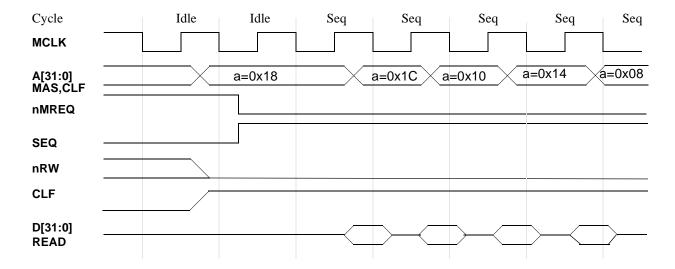

| 6 Cache Line Fill                                       | 35 |

| 7 Read-Lock-Write                                       | 36 |

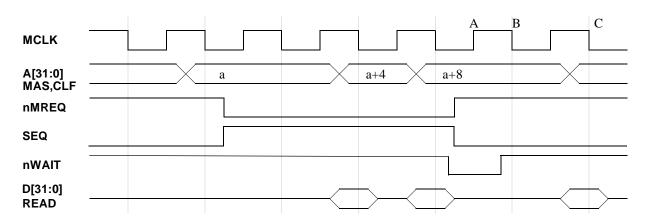

| 8 Using nWAIT to Stop the SA-110 for One MCLK Cycle     | 36 |

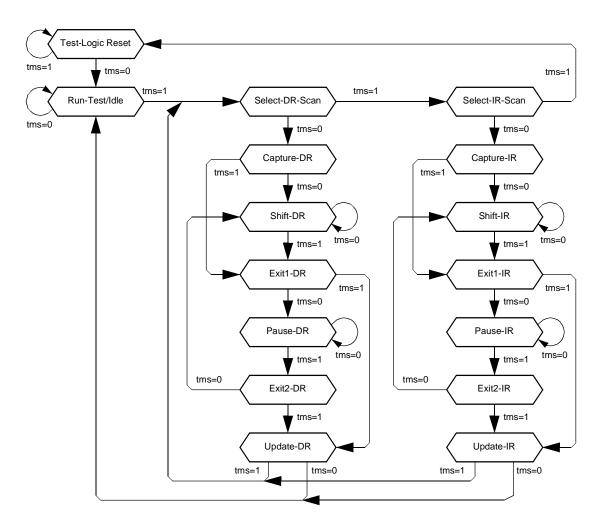

| 9 Test Access Port (TAP) Controller State Transitions   | 40 |

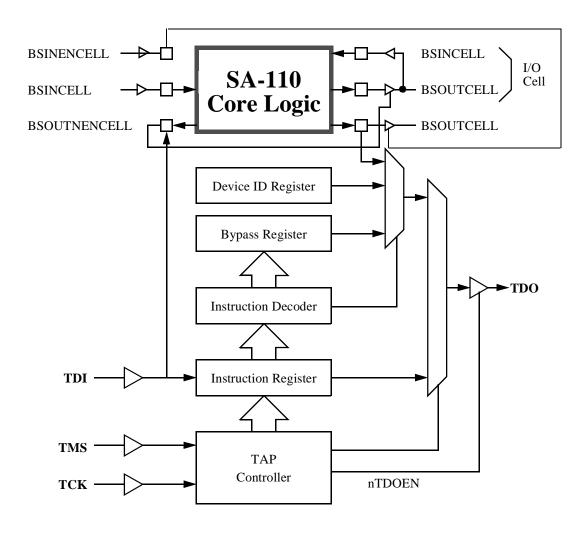

| 10 Boundary Scan Block Diagram                          | 44 |

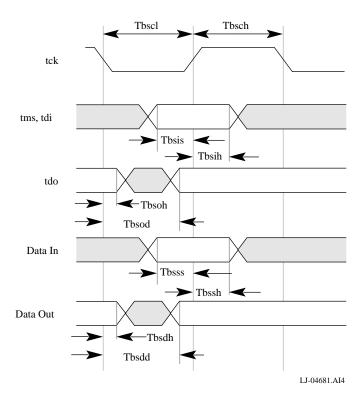

| 11 Boundary Scan General Timing                         | 46 |

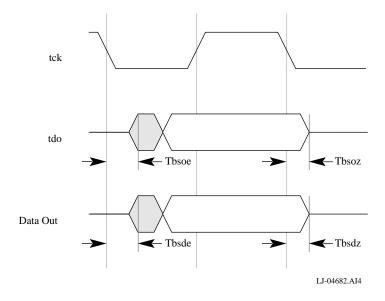

| 12 Boundary Scan Tri-state Timing                       |    |

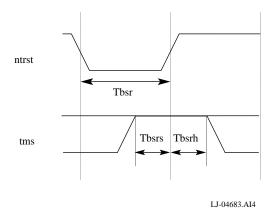

| 13 Boundary Scan Reset Timing                           | 47 |

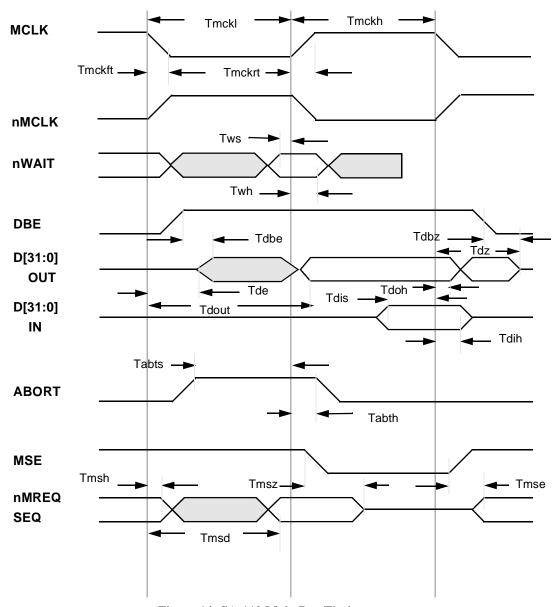

| 14 SA-110 Main Bus Timing                               |    |

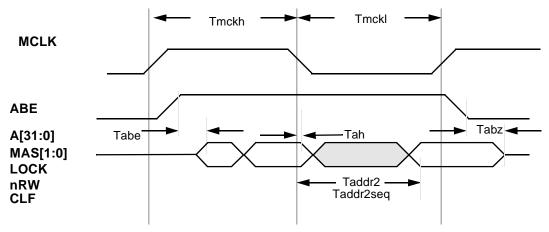

| 15 SA-110 Address Timing with APE=Low                   | 55 |

| 16 SA-110 Address Timing with APE=HIGH                  | 55 |

| 17 SA-110 144-Pin TQFP Mechanical Dimensions in mm      | 62 |

# **Tables**

| 1 S | Signal Pin Description                        | 5  |

|-----|-----------------------------------------------|----|

| 2 V | Vector Summary                                | 10 |

| 3 I | nstruction Timings                            | 12 |

| 4 ( | Cache & MMU Control Registers                 | 14 |

| 5 ( | Cache Control Operations                      | 17 |

| 6 7 | FLB Control Operations                        | 17 |

| 7 ' | Test, Clock, and Idle Controls                | 18 |

| 8 V | Valid MMU, Dcache & Write Buffer Combinations | 25 |

| 9 ( | CCLK Configurations                           | 28 |

| 10  | MCLK Configurations                           | 29 |

| 11  | Enhanced Mode Wrapping Order                  | 30 |

| 12  | Byte Mask                                     | 31 |

| 13  | Cycle Type Encodings                          | 32 |

| 14  | SA-110 Transactions                           | 37 |

| 15  | SA-110 Boundary Scan Interface Timing         | 48 |

| 16  | Boundary Scan Signals & Pins                  | 49 |

| 17  | SA-110 dc Maximum Ratings                     | 51 |

| 18  | SA-110 dc Operating Conditions                | 51 |

| 19  | SA-110 dc Characteristics                     | 52 |

| 20  | SA-110 Power Supply Voltages and Currents     | 52 |

| 21  | SA-110 Output Derating                        | 53 |

| 22  | SA-110 ac for –AA Parts                       | 57 |

| 23  | SA-110 ac for –BA Parts                       | 58 |

| 24  | SA-110 ac for -CA Parts                       | 59 |

| 25  | SA-110 ac for –DA Parts                       | 60 |

| 26  | SA-110 ac for –EA Parts                       | 61 |

| 27  | SA-110 Pinout – 144 pin Thin Quad Flat Pack   | 63 |

## 1.0 Introduction

The SA-110 microprocessor (SA-110) is a general purpose 32-bit microprocessor with a 16KB instruction cache, a 16KB writeback data cache, an 8-entry write buffer with 16 bytes per entry, and a memory management unit (MMU) combined in a single chip. The SA-110 is software compatible with the ARM V4 architecture processor family and can be used with ARM support chips such as I/O, memory and video.

The onchip caches together with the write buffer substantially raise the average execution speed and reduce the average amount of memory bandwidth required by the processor. This allows the external memory to support additional processors or direct memory access (DMA) channels with minimal performance loss.

The instruction set comprises eight basic instruction types:

- Two of these make use of the onchip arithmetic logic unit, barrel shifter and multiplier to perform high-speed operations on the data in a bank of 16 logical (31 physical) registers, each 32 bits wide.

- Three classes of instructions control data transfer between memory and the registers, one optimized for flexibility of addressing, another for rapid context switching and the third for swapping data.

- Two instructions control the flow and privilege level of execution.

- One class is used to access the privileged state of the machine.

The ARM instruction set is a good target for compilers of many different high-level languages. Assembly code programming, where required for critical code segments, is also straightforward unlike some RISC processors which depend on sophisticated compiler technology to manage complicated instruction interdependencies.

The memory interface has been designed to allow the performance potential to be realized without incurring high costs in the memory system. Speed-critical control signals are pipelined to allow system control functions to be implemented in standard low-power logic, and these control signals permit the exploitation of page mode access offered by industry standard DRAMs.

The SA-110 is a static part and has been designed to run at a reduced voltage to minimize its power requirements. This makes it ideal for portable applications where both these features are essential.

#### **Document Conventions:**

0x - marks a Hexadecimal quantity

**BOLD** - external signals are shown in bold capital letters

binary - where it is not clear that a quantity is binary it is followed by the word binary.

## Introduction

#### 1.1 ARM Architecture

The SA-110 implements the ARM V4 architecture as defined in the ARM Architecture Reference, Version A, 7 Feb. 1996, with the following options.

#### 1.1.1 26-Bit Mode

The SA-110 supports 26-bit mode but all exceptions are initiated in 32-bit mode. The P and D bits do not affect the operation of SA-110; they always read as a one and writes to them are ignored.

#### 1.1.2 Coprocessors

The SA-110 only supports MCR and MRC access to coprocessor number 15. These instructions are used to access the memory management, configuration, and cache control registers. All other coprocessor instructions cause an undefined instruction exception. No support for external coprocessors is provided.

### 1.1.3 Memory Management

Memory management exceptions preserve the base address registers so no *fixup* code is required. Separate translation look aside buffers (TLBs) are implemented for the instruction and data streams. The TLBs each have 32 entries that can each map a segment, a large page, or a small page. The TLB replacement algorithm is round robin. The data TLBs support both the flush-all and flush-single-entry operation, while the instruction TLBs only support the flush-all operation.

#### 1.1.4 Instruction Cache

The SA-110 has a 16KB instruction cache (Icache) with 32-byte blocks and 32-way associativity. The Icache supports the flush-all-entry function. Replacement is round robin within a set. The Icache can be enabled while memory management is disabled. When memory management is disabled all of memory is considered cacheable by the Icache.

#### 1.1.5 Data Cache

SA-110 has a 16KB data cache (Dcache) with 32-byte blocks and 32-way associativity. The Dcache supports the flush-all, flush-entry, and copyback-entry functions. The copyback-all function is not supported in hardware. This function can be provided by software. The cache is read allocate with round-robin replacement.

#### 1.1.6 Write Buffer

The SA-110 has a 8-entry write buffer with each entry able to contain 1 to 16 bytes. The drain-writebuffer operation is supported.

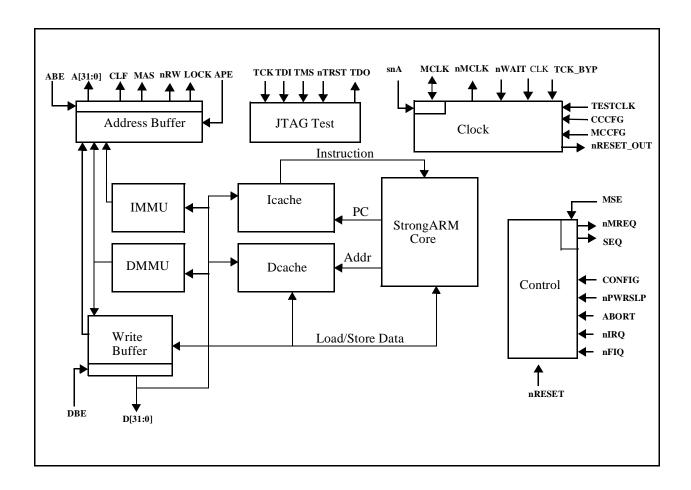

# 1.2 Block Diagram

Figure 1: SA-110 Block Diagram

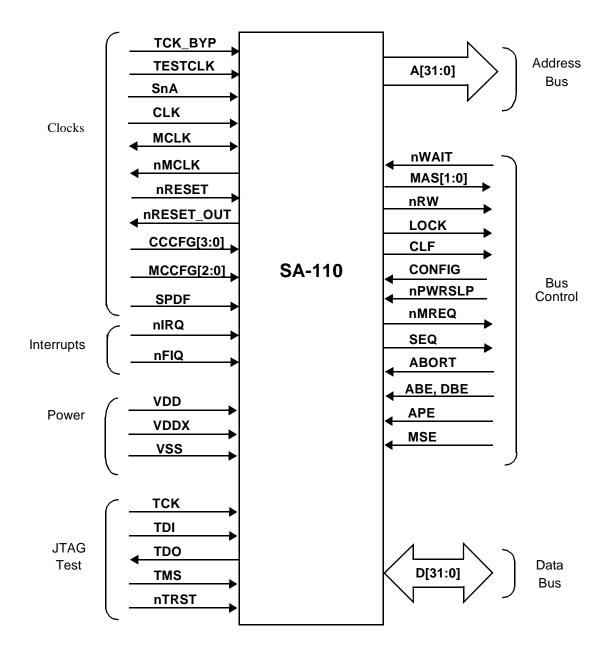

# 1.3 Functional Diagram

Figure 2: Functional Diagram

# 2.0 Signal Description

**Table 1: Signal Pin Description**

| Name       | Type  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A[31:0]    | OCZ   | Address Bus. This bus signals the address requested for memory accesses. If <b>APE</b> is high the address changes while <b>MCLK</b> is high, if <b>APE</b> is low the address changes during the following low period of <b>MCLK</b> . In enhanced bus mode <b>A[1:0]</b> contain byte mask bits two and three. The byte mask bits are asserted low on reads to indicate the required data. The byte mask bits are asserted low on writes to signal which bytes of the 32-bit data bus contain data to be accessed. In standard mode <b>A[1:0]</b> contain the low order two bits of the address. In both modes <b>A[31:2]</b> contain the upper 30 bits of the byte address. |  |

| ABE        | IC    | Address bus enable. When this input is low, the address bus A[31:0], nRW, MAS[1:0], CLF, and LOCK are put into a high impedance state (Note 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| ABORT      | IC    | External abort. Allows the memory system to tell the processor that a requested access has failed. Only monitored when the SA-110 is accessing external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| APE        | IC    | Address pipeline enable. This input is used to control the timing of the latches on the address bus A[31:0], MAS[1:0], nRW, CLF, and LOCK. Normally these signals change during MCLK high, but they may be held to the next MCLK low by driving APE low. APE is a static configuration pin and must remain stable at all times.                                                                                                                                                                                                                                                                                                                                                |  |

| CCCFG[3:0] | IC    | Core Clock Configuration pins. These four pins configure the core clock speed. They must remain stable at all times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CLF        | OCZ   | Cache Line Fill. An output signal used by the processor to indicate a cache line fill burst read or write. The <b>CLF</b> pin is asserted for full 8-word reads and writes. Burst reads are only done for cache line fills. Burst writes are done for castouts of dirty data and data stores that have merged in the write buffer. If <b>CONFIG</b> is high, then cache line fetches are wrapped in the four word subblock and then switched to the other subblock. The <b>CLF</b> signal follows address bus timing. Note it is NOT asserted for writes in pass one parts.                                                                                                    |  |

| CLK        | IC    | The 3.57/3.68 MHZ crystal oscillator input clock for the core PLL. This is the base clock in from which the high speed core clock and the <b>MCLK</b> in synchronous mode are generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| CONFIG     | IC    | The <b>CONFIG</b> input sets the bus mode to standard (low) or enhanced (high). In standard mode all cache line fetches start at word 0 of the cache block and stores are not allowed to merge. If <b>CONFIG</b> is high then cache line fetches are wrapped in the four word subblock then switch to the other subblock starting at the critical word. The write buffer is allowed to merge stores to the same cache block and will use the <b>A[1:0]</b> and <b>MAS[1:0]</b> pins to present a byte mask of the bytes being read or written. The <b>CONFIG</b> signal must remain stable at all times.                                                                       |  |

| D[31:0]    | ICOCZ | Data bus. These are bi-directional pins used for data transfers between the processor and external memory. For read operations (when <b>nRW</b> is low), the input data must be valid before the falling edge of <b>MCLK</b> . For write operations (when <b>nRW</b> is high), the output data will become valid while <b>MCLK</b> is low.                                                                                                                                                                                                                                                                                                                                     |  |

| DBE        | IC    | Data bus enable. When this input is low, the data bus, <b>D[31:0]</b> is put into a high impedance state (Note 1). The drivers will always be high impedance except during write operations, and <b>DBE</b> must be driven high in systems which do not require the data bus for DMA or similar activities.                                                                                                                                                                                                                                                                                                                                                                    |  |

**Table 1: Signal Pin Description**

| Name       | Type  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LOCK       | OCZ   | Locked operation. LOCK is driven high, to signal a "locked" memory access sequence, and the memory manager should wait until LOCK goes low before allowing another device to access the memory. LOCK changes while MCLK is high and remains high during the locked memory sequence. The LOCK signal follows address bus timing.                                                                                                                                                                                                                                                                                                   |  |

| MAS[1:0]   | OCZ   | Memory access size. An output signal used by the processor in standard bus mode to indicate to the external memory system the number of bytes being transferred. MAS[1:0] is 2 for word transfers, 1 for halfword transfers, and 0 for byte transfers, and is valid for both read and write operations. In enhanced mode the MAS pins contain bits zero and one of the byte mask. The byte mask bits are asserted low on reads to indicate the required data. The byte masks bits are asserted low on writes to signal which bytes of the 32-bit data bus contain data to be accessed. The MAS signals follow address bus timing. |  |

| MCCFG[2:0] | IC    | Memory Clock Configuration pins. These pins configure the system clock speed when <b>SnA</b> is asserted. They must remain stable at all times and may not be dynamically changed. When <b>SnA</b> is asserted <b>MCLK</b> is generated by dividing the core clock by the value of <b>MCCFG</b> plus two (29) for <b>MCCFG</b> in the range 07.                                                                                                                                                                                                                                                                                   |  |

| MCLK       | ICOCZ | Memory clock input or output. When <b>SnA</b> is deasserted <b>MCLK</b> is an input clock, when <b>SnA</b> is asserted <b>MCLK</b> is an output. This clock times all <b>SA-110</b> memory accesses. The low or high period of <b>MCLK</b> may be stretched for slow peripherals; alternatively, the <b>nWAIT</b> input may be used with a free-running <b>MCLK</b> to achieve similar effects.                                                                                                                                                                                                                                   |  |

| MSE        | IC    | Memory request/sequential enable. When this input is low, the <b>nMREQ</b> and <b>SEQ</b> outputs are put into a high impedance state (Note 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| nFIQ       | IC    | Not fast interrupt request. If <b>FIQ</b> s are enabled, the processor will respond to a low level on this input by taking the <b>FIQ</b> interrupt exception. This is an asynchronous, level-sensitive input, and must be held low until a suitable response is received from the processor.                                                                                                                                                                                                                                                                                                                                     |  |

| nIRQ       | IC    | Not interrupt request. As <b>nFIQ</b> , but with lower priority. This is an asynchronous, level-sensitive input, and must be held low until a suitable response is received from the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| nMCLK      | OCZ   | Not memory clock output. When <b>SnA</b> is high, <b>nMCLK</b> is the inverse of <b>MCLK</b> . If <b>SnA</b> is low then <b>nMCLK</b> is held low. This output can also be disabled by an MCR instruction to save power if <b>nMCLK</b> is not used.                                                                                                                                                                                                                                                                                                                                                                              |  |

| nMREQ      | OCZ   | Not memory request. A pipelined signal that changes while <b>MCLK</b> is low to indicate whether or not, in the following cycle, the processor will be accessing external memory. When <b>nMREQ</b> is low, the processor will be accessing external memory.                                                                                                                                                                                                                                                                                                                                                                      |  |

| nPWRSLP    | IC    | Power Sleep. When low this puts the SA-110 I/O pins into sleep mode. In sleep mode all outputs are driven low except <b>nMREQ</b> which is driven high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| nRESET     | IC    | Not reset. This is a level sensitive input which is used to start the processor from a known address. A low level will cause the current instruction to terminate abnormally, and the onchip caches, MMU, and write buffer to be disabled. When <b>nRESET</b> is driven high, the processor will re-start from address 0. <b>nRESET</b> must remain low for at least 2 full <b>MCLK</b> cycles. While <b>nRESET</b> is low the processor will perform idle cycles.                                                                                                                                                                |  |

| nRESET_OUT | OCZ   | Not reset out. This signal is asserted when <b>nRESET</b> is asserted and deasserts when the processor has completed resetting. This signal remains asserted until the PLL is stable.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

**Table 1: Signal Pin Description**

| Name    | Туре | Description                                                                                                                                                                                                                                                                                                                                                    |  |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| nRW     | OCZ  | Not read/write. When high this signal indicates a processor write operation; when low, a read. The <b>nRW</b> signal follows address bus timing.                                                                                                                                                                                                               |  |

| nTRST   | IC   | Test interface reset. Note this pin does NOT have an internal pullup resistor. This pin must be pulsed or driven low to achieve normal device operation, in addition to the normal device reset (nRESET).                                                                                                                                                      |  |

| nWAIT   | IC   | Not wait. When low this allows extra MCLK cycles to be inserted in memory accesses. It must be asserted low before the rising edge of MCLK to extend the MCLK cycle and is latched with the rising edge of MCLK. Note this is different than previous ARM processors that required nWAIT to be asserted for the entire MCLK high time and did not latch nWAIT. |  |

| SEQ     | OCZ  | Sequential address. This signal is the inverse of <b>nMREQ</b> , and is provided for compatibility with existing ARM memory systems. The signal changes while <b>MCLK</b> is high.                                                                                                                                                                             |  |

| SnA     | IC   | Synchronous/Not Asynchronous. When <b>SnA</b> is low, MCLK is an input and <b>nMCLK</b> is driven low. When <b>SnA</b> is high, <b>nMCLK</b> and <b>MCLK</b> are output clocks with the frequency selected by the <b>MCCFG</b> and <b>CCCFG</b> pins. <b>SnA</b> must remain stable at all times and may not be dynamically changed.                           |  |

| SPDF    | IC   | SPDF. The SPDF pin should be tied low. It is for DIGITAL use only.                                                                                                                                                                                                                                                                                             |  |

| TCK     | IC   | Test interface reference Clock. This times all the transfers on the JTAG test interface.                                                                                                                                                                                                                                                                       |  |

| TCK_BYP | IC   | Test clock PLL bypass. When <b>TCK_BYP</b> is high, the <b>TESTCLK</b> is used as the core clock in place of the PLL clock, when low the internal PLL output is used.                                                                                                                                                                                          |  |

| TDI     | IC   | Test interface data input. Note this pin does NOT have an internal pullup resistor.                                                                                                                                                                                                                                                                            |  |

| TDO     | OCZ  | Test interface data output. Note this pin does NOT have an internal pullup resistor.                                                                                                                                                                                                                                                                           |  |

| TESTCLK | IC   | Test Clock. <b>TESTCLK</b> is used to provide the core clock when <b>TCK_BYP</b> is high. It should be tied low if <b>TCK_BYP</b> is low. This clock should never be driven higher than <b>VDD</b> .                                                                                                                                                           |  |

| TMS     | IC   | Test interface mode select. Note this pin does NOT have an internal pullup resistor.                                                                                                                                                                                                                                                                           |  |

| VDD     |      | Positive supply for the core. Eight pins are allocated to <b>VDD</b> .                                                                                                                                                                                                                                                                                         |  |

| VDDX    |      | Positive supply for the I/O pins. Nine pins are allocated to <b>VDDX</b> .                                                                                                                                                                                                                                                                                     |  |

| VSS     |      | Ground supply. Eighteen pins are allocated to <b>VSS</b> . The ground plane on the board should be the same for these pins.                                                                                                                                                                                                                                    |  |

#### **Notes:**

- 1. When output pads are placed in the high impedance state for long periods, care must be taken to ensure that they do not float to an undefined logic level, as this can dissipate power, especially in the pads.

- 2. It must be noted that unless all inputs are driven to the **VSS** or **VDDX**, the input circuits will consume power.

**Key to Signal Types:** IC – Input, CMOS threshold

ICOCZ – Input, CMOS threshold, output CMOS levels, tri-stateable

OCZ – Output, CMOS levels, tri-stateable

# 3.0 ARM Implementation Options

The following sections describe ARM architecture options that are implemented by the SA-110.

#### 3.1 Big and Little Endian

The big endian bit, in the control register, sets whether the SA-110 treats words in memory as being stored in big endian or little endian format. Memory is viewed as a linear collection of bytes numbered upwards from 0. Bytes 0 to 3 hold the first stored word, bytes 4 to 7 the second and so on.

In the little endian scheme the lowest numbered byte in a word is considered to be the least significant byte of the word and the highest numbered byte is the most significant. Byte 0 of the memory system should be connected to data lines 7 through 0 (**D[7:0**]) in this scheme.

In the big endian scheme the most significant byte of a word is stored at the lowest numbered byte and the least significant byte is stored at the highest numbered byte. Byte 0 of the memory system should therefore be connected to data lines 31 through 24 (**D**[31:24]).

The state of the big endian bit only changes the location of the bytes within a 32-bit word. The accessed bytes are changed for the load byte, store byte, load halfword, and store halfword instructions only. Instruction fetches and word load and stores are not changed by the state of the bigend bit.

### 3.2 Exceptions

Exceptions arise whenever there is a need for the normal flow of program execution to be broken, so that (for example) the processor can be diverted to handle an interrupt from a peripheral. The processor state just prior to handling the exception must be preserved so that the original program can be resumed when the exception routine has completed. Many exceptions may arise at the same time.

The SA-110 handles exceptions by making use of the banked registers to save state. The old PC and CPSR contents are copied into the appropriate R14 and SPSR and the PC and mode bits in the CPSR bits are forced to a value which depends on the exception. Interrupt disable flags are set where required to prevent otherwise unmanageable nestings of exceptions. In the case of a re-entrant interrupt handler, R14 and the SPSR should be saved onto a stack in main memory before re-enabling the interrupt; when transferring the SPSR register to and from a stack, it is important to transfer the whole 32 bit value, and not just the flag or control fields.

When multiple exceptions arise simultaneously, a fixed priority determines the order in which they are handled. The priorities are listed later in this chapter. Most exceptions are fully defined in the *ARM Architecture Reference*. The following sections specify the exceptions where the SA-110 implementation differs from the *ARM Architecture Reference*.

The SA-110 initiates all exceptions in 32-bit mode. When an exception occurs while the SA-110 is running in 26-bit mode the SA-110 saves only the PC and CPSR. The PC is saved in R14 and the CPSR is saved in the SPSR of the exception mode. The 32-bit handler will have to merge the condition codes, the interrupt enables, and the mode from the SPSR into R14 if a handler wants to run in 26-bit mode.

#### 3.2.1 Reset

When the **nRESET** signal goes low, the SA-110 stops executing instructions, asserts the **nRESET\_OUT** pin, and then performs idle cycles on the bus.

When **nRESET** goes high again, the SA-110 does the following:

- (1) Overwrites R14\_svc and SPSR\_svc by copying the current values of the PC and CPSR into them. The values of the saved PC and CPSR are not defined.

- (2) Forces M[4:0]=10011 (32-bit Supervisor mode) and sets the I and F bits in the CPSR.

- (3) Forces the PC to fetch the next instruction from address 0x0

At the end of the reset sequence, the MMU, Icache, Dcache, and write buffer are disabled. Alignment faults are also disabled, and little endian mode is enabled.

#### **3.2.2 Abort**

An abort can be signalled by either the internal memory management unit or from the external **ABORT** input pin. **ABORT** indicates that the current memory access cannot be completed. For instance, in a virtual memory system the data corresponding to the current address may have been moved out of memory onto a disk, and considerable processor activity may be required to recover the data before the access can be performed successfully The SA-110 checks for **ABORT** during memory access cycles. When aborted the SA-110 will respond in one of two ways:

- (1) If the abort occurred during an instruction prefetch (a *prefetch abort*), the prefetched instruction is marked as invalid but the abort exception does not occur immediately. If the instruction is not executed, for example as a result of a branch being taken while it is in the pipeline, no abort will occur. An abort will take place if the instruction reaches the head of the pipeline and is about to be executed.

- (2) If the abort occurred during a data access (a *data abort*), the action depends on the instruction type.

- (a) Single data transfer instructions (LDR, STR) will abort with no registers modified.

- (b) The swap instruction (SWP) is aborted as though it had not executed, though externally the read access may take place.

- (c) Block data transfer instructions (LDM, STM) abort on the first access that cannot complete. If writeback is set, the base is **NOT** updated. If the instruction would normally have overwritten the base with data (for example, a LDM instruction with the base in the transfer list), the original value in the base register is restored.

When either a prefetch or data abort occurs, the SA-110 performs the following operations:

- (1) Saves the address of the aborted instruction plus 4 (for prefetch aborts) or 8 (for data aborts) in R14\_abt; saves CPSR in SPSR abt.

- (2) Forces M[4:0]=10111 (Abort mode) and sets the I bit in the CPSR.

- (3) Forces the PC to fetch the next instruction from either address 0x0C (prefetch abort) or address 0x10 (data abort).

To return after fixing the reason for the abort, use SUBS PC, R14\_abt,#4 (for a prefetch abort) or SUBS PC,R14\_abt,#8 (for a data abort). This will restore both the PC and the CPSR and retry the aborted instruction.

The abort mechanism allows a *demand paged virtual memory system* to be implemented when suitable memory management software is available. The processor is allowed to generate arbitrary addresses, and when the data at an address is unavailable the MMU signals an abort. The processor traps into system software which must work out the cause of the abort, make the requested data available, and retry the aborted instruction. The application program needs no knowledge of the amount of memory available to it, nor is its state in any way affected by the abort.

#### 3.2.3 Vector Summary

**Table 2: Vector Summary**

| Address    | Exception             | Mode on entry |

|------------|-----------------------|---------------|

| 0x00000000 | Reset                 | Supervisor    |

| 0x00000004 | Undefined instruction | Undefined     |

| 0x00000008 | Software interrupt    | Supervisor    |

| 0x000000C  | Abort (prefetch)      | Abort         |

| 0x00000010 | Abort (data)          | Abort         |

| 0x00000014 | not used              |               |

| 0x00000018 | IRQ                   | IRQ           |

| 0x0000001C | FIQ                   | FIQ           |

These are byte addresses, and will normally contain a branch instruction pointing to the relevant routine.

#### 3.2.4 Exception Priorities

When multiple exceptions arise at the same time, a fixed priority system determines the order in which they will be handled:

- (1) Reset (highest priority)

- (2) Data abort

- (3) FIQ

- (4) IRQ

- (5) Prefetch abort

- (6) Undefined Instruction, software interrupt (lowest priority)

Note that not all exceptions can occur at once. Undefined instruction and software interrupt are mutually exclusive since they each correspond to particular (non-overlapping) decodings of the current instruction.

If a data abort occurs at the same time as a FIQ, and FIQs are enabled (that is, the F flag in the CPSR is clear), the SA-110 will enter the data abort handler and then immediately proceed to the FIQ vector. A normal return from FIQ will cause the data abort handler to resume execution. Placing data abort at a higher priority than FIQ is necessary to ensure that the transfer error does not escape detection; the time for this exception entry should be added to worst case FIQ latency calculations.

### 3.2.5 Interrupt Latencies

Calculating the worst-case interrupt latency for the SA-110 is quite complex (due to the cache, MMU, and write buffer) and is dependent on the configuration of the whole system.

### 3.3 Coprocessors

The SA-110 has no external coprocessor bus, so it is not possible to add external coprocessors to this device.

SA-110 uses the internal coprocessor designated #15 for control of the on chip MMU, Caches, and clocks. If a coprocessor other than #15 is accessed, then the CPU will take the undefined instruction trap. The coprocessor load, store, and data operation instructions also take the undefined instruction trap.

# 4.0 Instruction Set

#### **4.1 Instruction Set**

The SA-110 implements the ARM V4 architecture as defined in the ARM Architecture Reference, Version A, dated 7 Feb 1996, with previously noted options.

# **4.2 Instruction Timings**

The following table lists the instruction timing for the SA-110. The result delay is the number of cycles the next sequential instruction would stall if it used the result as an input. The issue cycles is the number of cycles this instruction takes to issue. For most instructions the result delay is zero and the issue cycles is one. For load and stores the timing is for cache hits.

**Table 3: Instruction Timings**

| Instruction group                          | Result delay | Issue Cycles                       |

|--------------------------------------------|--------------|------------------------------------|

| Data processing shift amount literal       | 0            | 1                                  |

| Data processing shift amount from register | 0            | 2                                  |

| Mul or Mul/Add giving 32-bit result        | 13           | 1                                  |

| Mul or Mul/Add giving 64-bit result        | 13           | 2                                  |

| Load Single – writeback of base            | 0            | 1                                  |

| Load Single – load data zero extended      | 1            | 1                                  |

| Load Single -load data sign extended       | 2            | 1                                  |

| Store Single – writeback of base           | 0            | 1                                  |

| Load Multiple (delay for last register)    | 1            | MAX(2, number of registers loaded) |

| Store Multiple – writeback of base         | 0            | MAX(2, number of registers loaded) |

| Branch or Branch and Link                  | 0            | 1                                  |

| MCR                                        | 2            | 1                                  |

| MRC                                        | 1            | 1                                  |

| MSR to control                             | 0            | 3                                  |

| MRS                                        | 0            | 1                                  |

| Swap                                       | 2            | 2                                  |

# **5.0 Configuration**

The operation and configuration of the SA-110 is controlled with coprocessor instructions, configuration pins, and with the memory management page tables. The coprocessor instructions manipulate on-chip registers which control the configuration of the cache, write buffer, MMU and a number of other configuration options.

Note: The gray areas in the register and translation diagrams are reserved and should be programmed 0 for future compatibility.

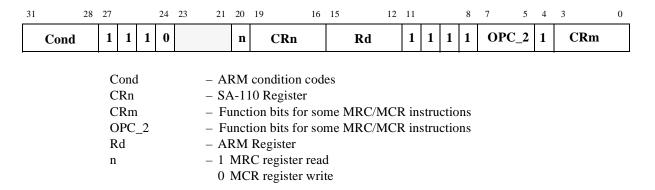

### 5.1 Internal Coprocessor Instructions

The on-chip registers may be read using MRC instructions and written using MCR instructions. These operations are only allowed in non-user modes and the undefined instruction trap will be taken if accesses are attempted in user mode.

Format of Internal Coprocessor Instructions MRC and MCR

# **5.2 Registers**

The SA-110 contains registers which control the cache and MMU operation. These registers are accessed using CPRT instructions to coprocessor #15 with the processor in any privileged mode. Only some of registers 0-15 are valid: the result of an access to an invalid register is unpredictable.

Table 4: Cache & MMU Control Registers

| Register | Register Reads         | Register Writes        |

|----------|------------------------|------------------------|

| 0        | ID Register            | Reserved               |

| 1        | Control                | Control                |

| 2        | Translation Table Base | Translation Table Base |

| 3        | Domain Access Control  | Domain Access Control  |

| 4        | Reserved               | Reserved               |

| 5        | Fault Status           | Fault Status           |

| 6        | Fault Address          | Fault Adress           |

| 7        | Reserved               | Cache Operations       |

| 8        | Reserved               | TLB Operations         |

| 914      | Reserved               | Reserved               |

| 15       | Reserved               | Test, clock, and Idle  |

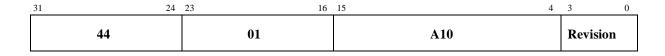

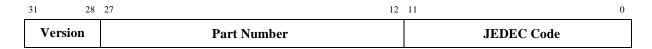

### **5.2.1** Register 0 – ID

Register 0 is a read-only register that returns the code for this chip: 0x4401A10x. The low order four bits of the register are the chip revision number.

### 5.2.2 Register 1 – Control

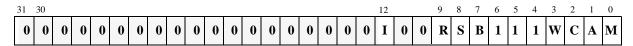

Register 1 is a read/write register containing control bits. All writeable bits in this register are forced low by reset.

#### M Bit 0 Enable/disable

0 – on-chip memory management unit disabled 1 – on-chip memory management unit enabled

#### A Bit 1 Address Fault Enable/Disable

0 – alignment fault disabled1 – alignment fault enabled

#### C Bit 2 Data Cache Enable/Disable

0 – Data cache disabled1 – Data cache enabled

#### W Bit 3 Write buffer Enable/Disable

0 – Write buffer disabled 1 – Write buffer enabled

#### B Bit 7 Big/Little Endian

0 – Little endian operation1 – Big endian operation

#### S Bit 8 System

This selects the access checks performed by the memory management unit. See the *ARM Architecture Reference* for more information.

#### R Bit 9 ROM

This selects the access checks performed by the memory management unit. See the *ARM Architecture Reference* for more information.

#### I Bit 12 Instruction Cache Enable/Disable

0 – Instruction cache disabled1 – Instruction cache enabled

#### Bit 13..31 Unused

Undefined on Read. Writes ignored.

# Configuration

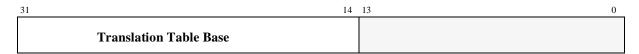

### **5.2.3 Register 2 – Translation Table Base**

Register 2 is a read/write register that holds the base of the currently active level one page table. Bits [13:0] are undefined on read, ignored on write.

### 5.2.4 Register 3 – Domain Access Control

Register 3 is a read/write register that holds the current access control for domains 0 to 15.

| 3 | 1 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|   | 1 | 5  | 1  | 4  | 1  | 13 | 1  | 12 | 1  | 11 | 1  | 10 |    | 9  |    | 8  |    | 7  | (  | 6  |    | 5  | 4 | 4 |   | 3 | , | 2 |   | 1 | ( | 0 |

#### 5.2.5 Register 4 – Reserved

Register 4 is reserved. Accessing this register has no effect.

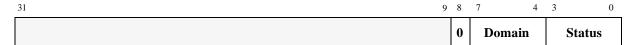

#### 5.2.6 Register 5 – Fault Status

Register 5 is a read/write register. Reading this register returns the current contents of the Fault Status Register (FSR). The FSR is written when a data memory fault occurs or can be written by a MCR to the FSR. It is not updated for a prefetch fault. See Chapter 7.0 Memory Management Unit (MMU) for more details. Bits [31:9] are undefined on read, ignored on write. Bit 8 is ignored on write and is always returned as zero.

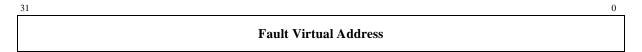

#### 5.2.7 Register 6 – Fault Address

#### Read/Write: Fault Address

Register 6 is a read/write register. Reading this register returns the current contents of the Fault Address Register (FAR). The FAR is written when a data memory fault occurs with the address of the data fault, or can be written by a MCR to the FAR.

# **5.2.8 Register 7 – Cache Control Operations**

Register 7 is a write-only register. The CRm and OPC\_2 fields are used to encode the cache control operations. All other values for OPC\_2 and CRm are unpredictable.

**Table 5: Cache Control Operations**

| Function             | OPC_2 | CRm    | Data            |

|----------------------|-------|--------|-----------------|

| Flush I+D            | 0b000 | 0b0111 | Ignored         |

| Flush I              | 0b000 | 0b0101 | Ignored         |

| Flush D              | 0b000 | 0b0110 | Ignored         |

| Flush D single entry | 0b001 | 0b0110 | Virtual Address |

| Clean D cache entry  | 0b001 | 0b1010 | Virtual Address |

| Drain Write Buffer   | 0b100 | 0b1010 | Ignored         |

#### 5.2.9 Register 8 – TLB Operations

Register 8 is a write-only register. The CRm and OPC\_2 fields are used to encode the following TLB flush operations. All other values for OPC\_2 and CRm are unpredictable.

**Table 6: TLB Control Operations**

| Function             | OPC_2 | CRm    | Data            |

|----------------------|-------|--------|-----------------|

| Flush I+D            | 0b000 | 0b0111 | Ignored         |

| Flush I              | 0b000 | 0b0101 | Ignored         |

| Flush D              | 0b000 | 0b0110 | Ignored         |

| Flush D single entry | 0b001 | 0b0110 | Virtual Address |

### 5.2.10 Registers 9 -14 Reserved

The results of accessing any of these registers is unpredictable.

# Configuration

#### 5.2.11 Registers 15 – Test, Clock and Idle Control

Register 15 is a write-only register. The CRm and OPC\_2 fields are used to encode the following control operations. All other values for OPC\_2 and CRm are unpredictable.

Table 7: Test, Clock, and Idle Controls

| Function                                | OPC_2 | CRm    |

|-----------------------------------------|-------|--------|

| Enable odd word loading of Icache LFSR  | 0b001 | 0b0001 |

| Enable even word loading of Icache LFSR | 0b001 | 0b0010 |

| Clear Icache LFSR                       | 0b001 | 0b0100 |

| Move LFSR to R14.Abort                  | 0b001 | 0b1000 |

| Enable clock switching                  | 0b010 | 0b0001 |

| Disable clock switching                 | 0b010 | 0b0010 |

| Disable nMCLK output                    | 0b010 | 0b0100 |

| Wait for interrupt                      | 0b010 | 0b1000 |

#### **5.2.11.1 Icache LFSR Controls**

The OPC\_2=1 functions are used to control the Icache linear feedback shift register (LFSR) which is used for manufacturing tests.

#### 5.2.11.2 Clock Controls

The four OPC\_2=2 functions are used to enable and disable **DCLK** switching, disabling the **nMCLK** output and disabling **MCLK** output and waiting for an interrupt. See Chapter 8.0 SA-110 Clocking for information on their use.

## **6.0 Caches and Write Buffer**

To reduce effective memory access time the SA-110 has an instruction cache, a data cache, and a write buffer. In general these are transparent to program execution. The following sections describe each of these and give all necessary programming information.

### **6.1 Instruction Cache (Icache)**

The SA-110 contains a 16KB instruction cache (Icache). The Icache has 512 lines of 32 bytes (8 words), arranged as a 32-way set-associative cache, and uses the virtual addresses generated by the processor core. The Icache is always reloaded a line at a time (8 words). It may be enabled or disabled via the SA-110 control register and is disabled by the **nRESET** pin. The operation of the cache, when memory management is enabled, is further controlled the *Cacheable* or C bit stored in the memory management page table (see Chapter 7.0 Memory Management Unit (MMU).). If memory management is disabled all addresses are marked as cacheable (C=1). When memory management is enabled the C bit in each page table entry can disable caching for an area of virtual memory.

#### 6.1.1 Icache Operation

In the SA-110 the Icache will be searched regardless of the state of the C bit, only reads that miss the Icache will be affected. If, on an Icache miss, the C bit is a one or the MMU is disabled, a cache line fill of 8 words will be performed and it will be placed in an Icache bank with a round-robin replacement algorithm. If, on a miss, the MMU is enabled and the C bit is a zero for the given virtual address, an external memory access for a single word will be performed and the Icache will not be written. The Icache should be enabled as soon as possible after reset for best performance.

#### **6.1.2 Icache Validity**

The Icache operates with virtual addresses, so care must be taken to ensure that its contents remain consistent with the virtual to physical mappings performed by the memory management unit. If the memory mappings are changed, the Icache validity must be ensured. The Icache is not coherent with stores to memory so programs that write cacheable instruction locations must ensure the Icache validity. Instruction fetches do not check the write buffer so data must not only be pushed out of the Icache but the write buffer must also be drained.

#### 6.1.2.1 Software Icache Flush

The entire Icache can be invalidated by writing to the SA-110 cache operations register (Register 7). The cache will be flushed immediately when the register is written, but note that the following four instruction fetches may come from the cache before the register is written.

#### 6.1.3 Icache Enable/Disable and Reset

The Icache is automatically disabled and flushed on **nRESET**. Once enabled, cacheable read accesses will cause lines to be placed in the Icache. If the Icache is subsequently disabled, no new lines will be placed in the Icache, but the Icache will still be searched and if the data is found it will be used by the processor. If the data in the Icache must not be used, then the Icache must be flushed.

#### 6.1.3.1 Enabling the Icache

To enable the Icache set bit 12 in control register. The MMU and Icache may be enabled simultaneously with a single control register write.

## **Caches and Write Buffer**

#### 6.1.3.2 Disabling the Icache

To disable the Icache clear bit 12 in control register.

#### **6.2** Data Cache (Dcache)

The SA-110 contains a 16KB writeback data cache (Dcache). The Dcache has 512 lines of 32 bytes (8 words), arranged as a 32-way set-associative cache, and uses the virtual addresses generated by the processor. A line also contains the physical address the block was fetched from and two dirty bits. There is a dirty bit associated with both the first and second half of the block. When a store hits in the Dcache the dirty bit associated with it is set. When a block is evicted from the Dcache the dirty bits are used to decide if all, half, or none of the block will be written back to memory using the physical address stored with the block. The Dcache is always reloaded a line at a time (8 words). It may be enabled or disabled via the SA-110 control register and is disabled on **nRESET**. The operation of the Dcache is further controlled by the *Cacheable* or C bit and the *Bufferable* or B bit stored in the memory management page table (see Chapter 7.0 Memory Management Unit (MMU).). For this reason, in order to use the Dcache, the MMU must be enabled. The two functions may however be enabled simultaneously, with a single write to the control register.

#### 6.2.1 Cacheable Bit – C

The cacheable bit determines whether data being read may be placed in the Dcache and used for subsequent read operations. Typically main memory will be marked as cacheable to improve system performance, and I/O space as noncacheable to stop the data being stored in SA-110's Dcache. [For example if the processor is polling a hardware flag in I/O space, it is important that the processor is forced to read data from the external peripheral, and not a copy of initial data held in the cache].

#### 6.2.2 Bufferable Bit - B

The bufferable bit does not affect writes that hit in the Dcache. If a store hits in the Dcache the store is assumed to be bufferable. Writebacks of dirty lines are treated as bufferable writes. See section 6.3 on page 22 for more information on the B bit.

#### **6.2.3 Deache Operation**

In the SA-110 the Dcache will be searched regardless of the state of the C bit, only reads that miss the Dcache will check the C bit. The C bit controls loading the Dcache on a miss not checking the Dcache on an access.

#### 6.2.3.1 Cacheable Reads C = 1

A cache line fill of 8 words will be performed and it will be placed in a Dcache bank with a round-robin replacement algorithm.

#### **6.2.3.2** Noncacheable Reads C = 0

An external memory access will be performed and the Dcache will not be written.

Note: Load Multiples to C=0 space do NOT perform a burst read.

#### 6.2.4 Dcache Validity

The Dcache operates with virtual addresses, so care must be taken to ensure that its contents remain consistent with the virtual to physical mappings performed by the memory management unit. If the memory mappings are changed, the Dcache validity must be ensured.

#### **6.2.4.1 Software Deache Flush**

SA-110 supports the flush and clean operations on single entries of the Dcache by writes to the cache operations regsiters. The flush whole cache is also supported. Note that since this is a writeback cache, in order to not lose data, a flush whole must be preceded by a sequence of loads to cause the cache to write back any dirty entries. The following code will cause the Dcache to flush all dirty entries.

```

;+

;Call:

R0 points to the start of a 16384-byte region of readable data used

only for this cache flushing routine. If this area is used for

by other code then 32K must be loaded and the flush MCR is not

not needed.

bl writeBackDcache

;Return:

R0, R1, R2 trashed

Data cache is clean

writeBackDcache

add

r1, r0, #16384

11

ldr

r2, [r0], #32

teq

r1. r0

bne

p15, 0, r0, c7, c6, 0

mcr

mov

pc, r14

```

#### 6.2.4.2 Doubly Mapped Space

Since the cache works with virtual addresses, it is assumed that every virtual address maps to a different physical address. If the same physical location is accessed by more than one virtual address, the cache cannot maintain consistency, since each virtual address will have a separate entry in the cache, and only one entry will be updated on a processor write operation. To avoid any cache inconsistencies, doubly-mapped virtual addresses should be marked as noncacheable.

#### 6.2.5 Dcache Enable/Disable and Reset

The Dcache is automatically disabled and flushed on **nRESET**. Once enabled, cacheable read accesses will cause lines to be placed in the cache. If subsequently disabled, no new lines will be placed in the cache, but it will still be searched and if the data is found it will be used by the processor. Write operations will continue to update the cache, thus maintaining consistency with the external memory. If the data in the cache must not be used, then the cache must be flushed.

## **Caches and Write Buffer**

#### 6.2.5.1 Enabling the Dcache

To enable the Dcache, make sure that the MMU is enabled first by setting bit 0 in Control Register, then enable the Dcache by setting bit 2 in Control Register. The MMU and Dcache may be enabled simultaneously with a single control register write.

#### 6.2.5.2 Disabling the Dcache

To disable the Dcache clear bit 2 in Control Register.

#### **6.3** Write Buffer (WB)

The SA-110 write buffer is provided to improve system performance. It can buffer up to eight blocks of data of 1 to 16 bytes, at independent addresses. It may be enabled or disabled via the W bit (bit 3) in the SA-110 control register and the buffer is disabled and all entries are marked empty on reset. The operation of the write buffer is further controlled by the *Cacheable* or C bit and the *Bufferable* or B bit, which are stored in the memory management page tables. For this reason, in order to use the write buffer, the MMU must be enabled. The two functions may however be enabled simultaneously, with a single write to the control register. For a write to use the write buffer, both the W bit in the control register, and the B bit in the corresponding page table must be set. It is not possible to abort buffered writes externally; the abort pin will be ignored.

#### 6.3.1 Bufferable Bit

This bit controls whether a write operation may use the write buffer. Typically main memory will be bufferable and I/O space unbufferable.

#### **6.3.2** Write Buffer Operation

When the CPU performs a store, the Dcache is first checked. If the Dcache hits on the store and the protection for the location and mode of the store allows the write then the write completes in the cache and the writebuffer is not used. If the location misses in the Dcache then the translation entry for that address is inspected and the state of the B and C bits determines which of the three following actions are performed. If the write buffer is disabled via the SA-110 Control Register, writes are treated as if the B bit is a zero.

#### 6.3.2.1 Writes to a Bufferable and Cacheable Location (B=1,C=1)

If the write buffer is enabled and the **CONFIG** pin is asserted and the processor performs a write to a bufferable and cacheable location, and the data is in the Dcache, then the data is written to the Dcache, and the Dcache line is marked dirty. If a write to a bufferable area misses in the data cache, the data is placed in the write buffer and the CPU continues execution. When placing the write data into the write buffer if the data is being written to the same 16 byte aligned area of the previous write then the current write is merged into the same entry in the write buffer. The write buffer performs the external write some time later. If a write is done and the write buffer is full then the processor is stalled until there is sufficient space in the buffer. If the **CONFIG** pin is not asserted then no merging is allowed.

#### 6.3.2.2 Writes to Bufferable and Noncacheable Location (B=1,C=0)